Next Design詳細

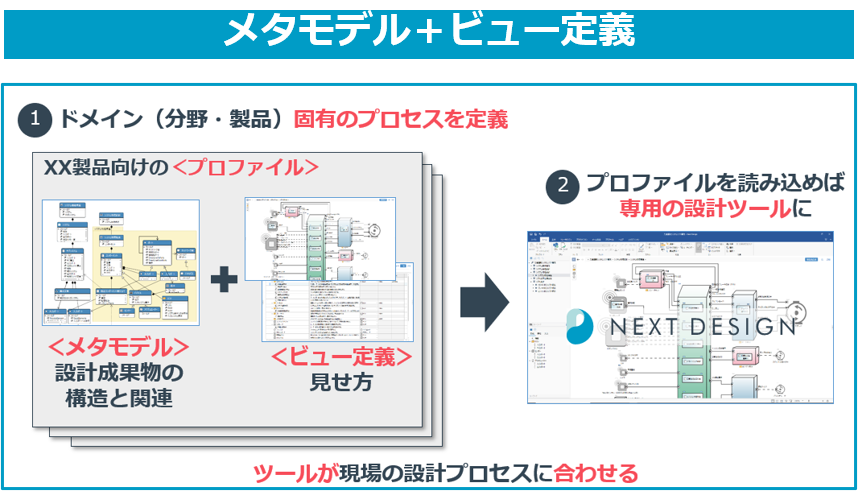

設計データをプロファイル化して開発現場にフィットする次世代設計ツール

- ・設計データの構造と関連を定義した「メタモデル」と設計情報の見せ方を定義した「ビュー」を開発プロセスごとにプロファイル化

- ・現場レベルにフィットしたプロファイルを利用することで製品ごとの異なるアーキテクチャや設計内容を具現化

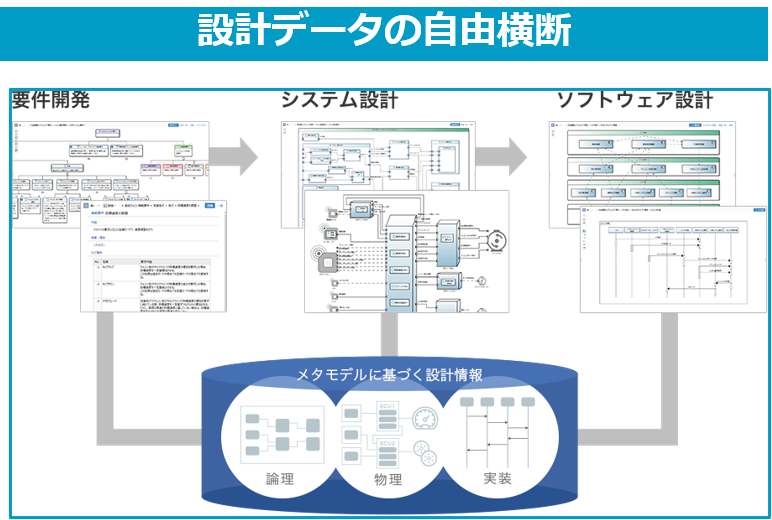

- ・メタモデルに基づいて設計されたデータはデジタル蓄積および一元化され、組織や企業間を横断して設計データを標準化・共有化

|

|

※クリックすると拡大画像が表示されます。

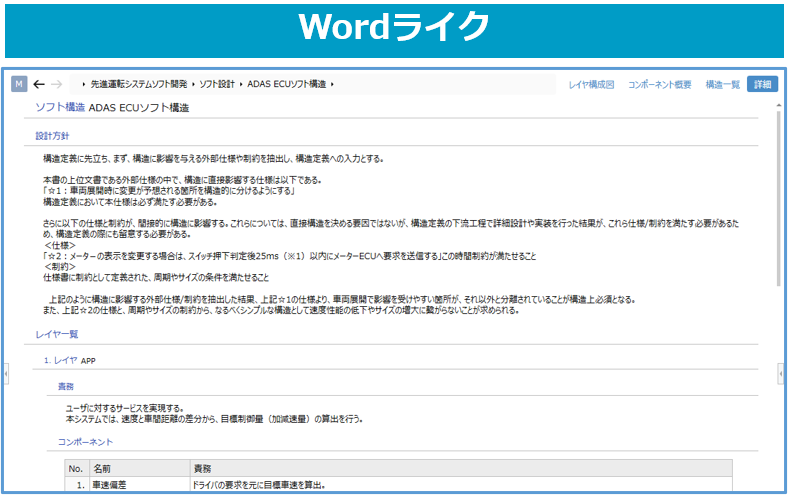

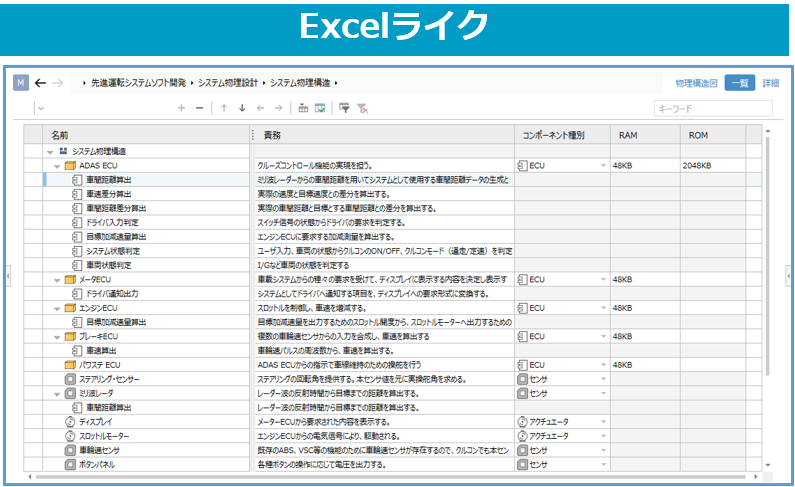

文書表現やダイアグラム表現などマルチな表現バリエーション

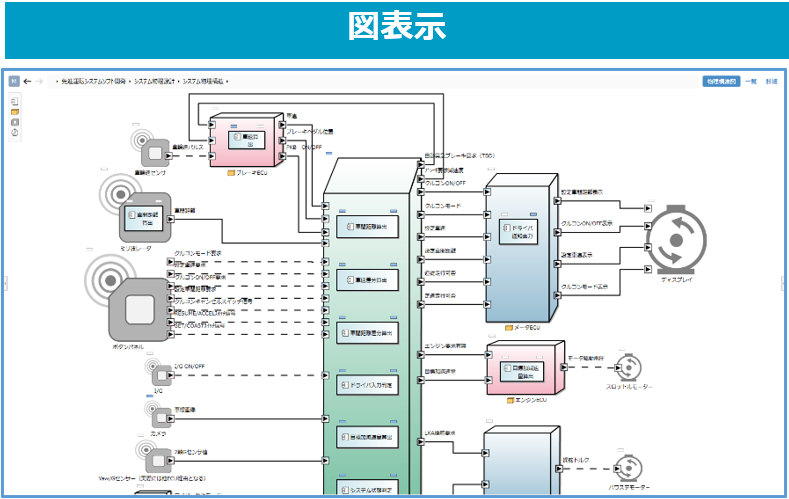

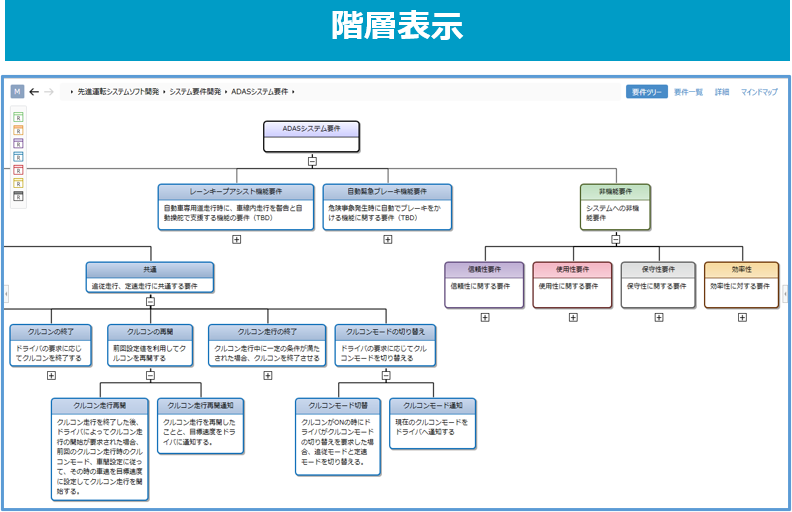

- ・設計情報の見え方(ビュー定義)を多彩な表現バリエーションに設定可能

- ・Wordライク表示、Excelライク表示、ダイアグラム表示、階層構造表示

- ・UML/SysML表現にも対応

|

|

|

|

|

※クリックすると拡大画像が表示されます。

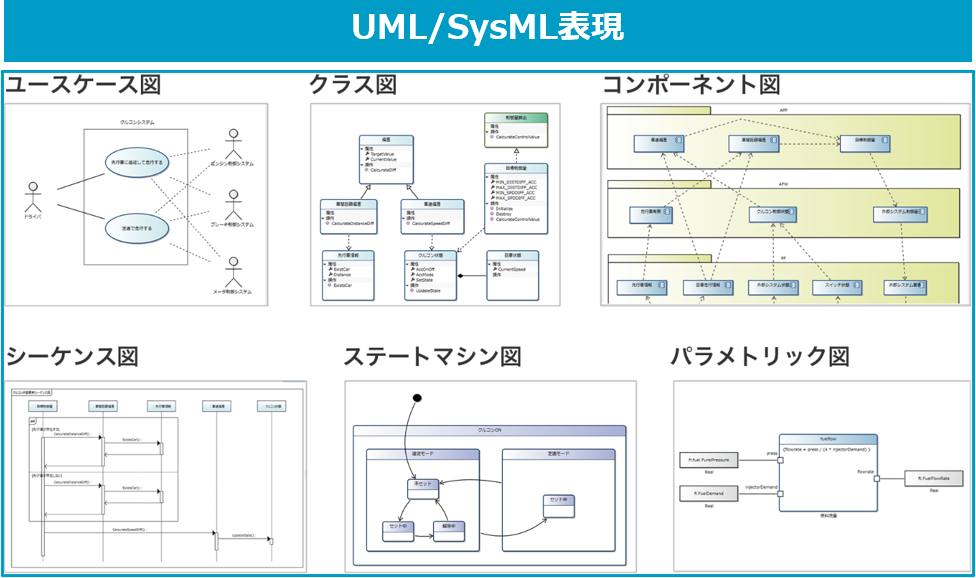

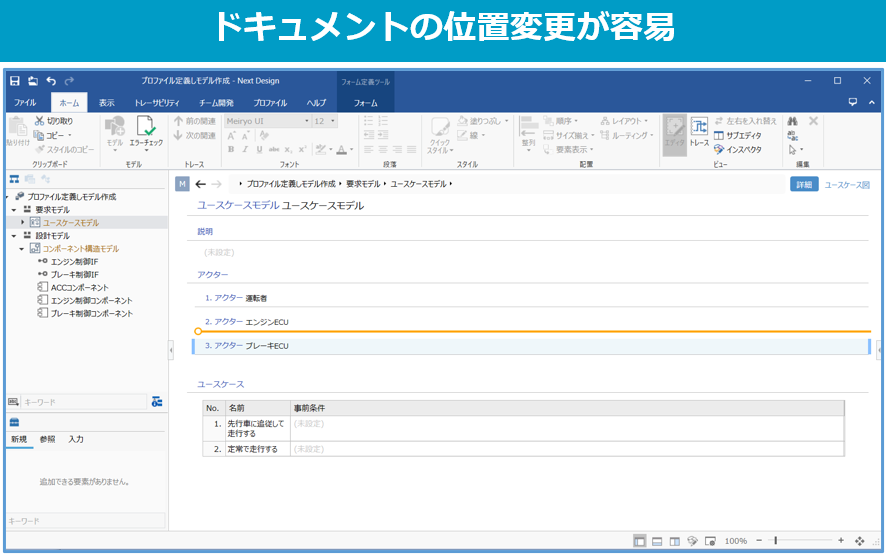

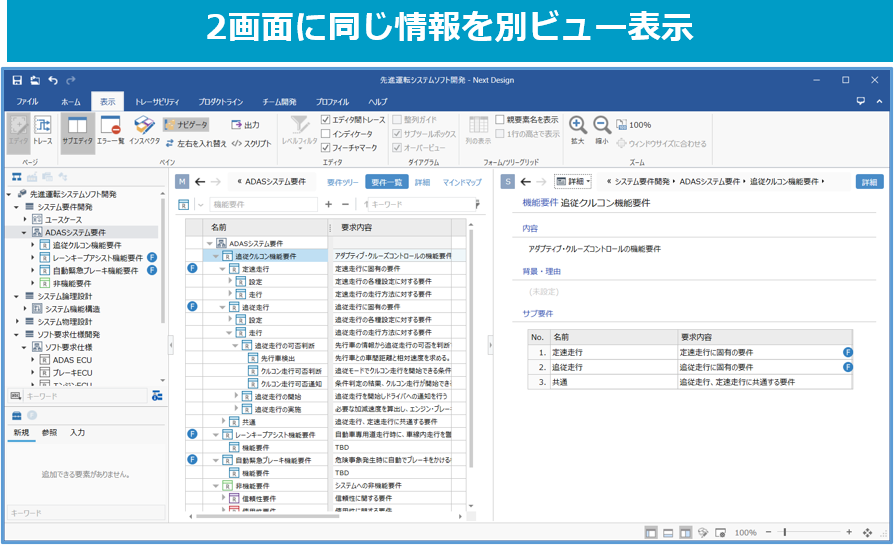

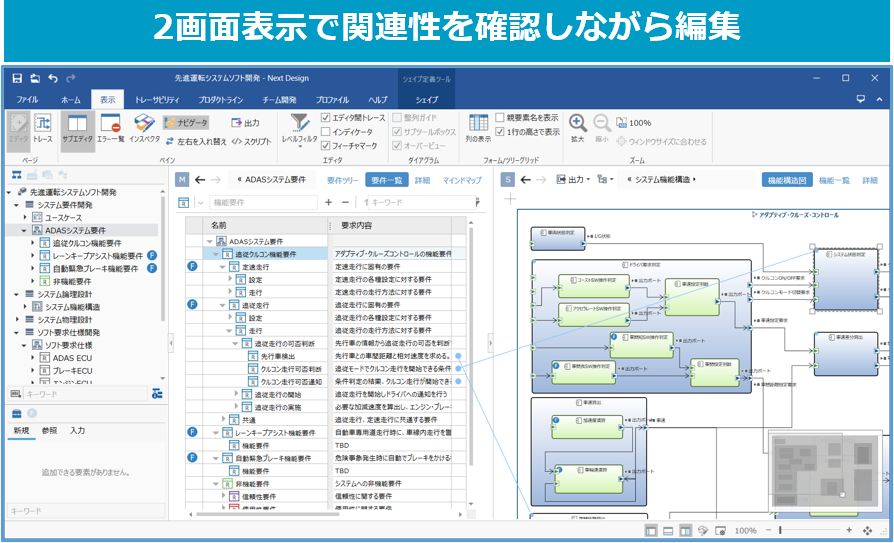

WordやExcelと同じ操作性で直感的な編集操作

- ・WordやExcelのようなリボンによる直観的な操作

- ・ドキュメントのフォームやツリーはドラッグドロップで位置変更が可能

- ・2画面表示により、モデル間の関係性などを全体俯瞰しながらもう一方で個々の詳細を文書を確認・編集が可能

|

|

|

|

※クリックすると拡大画像が表示されます。

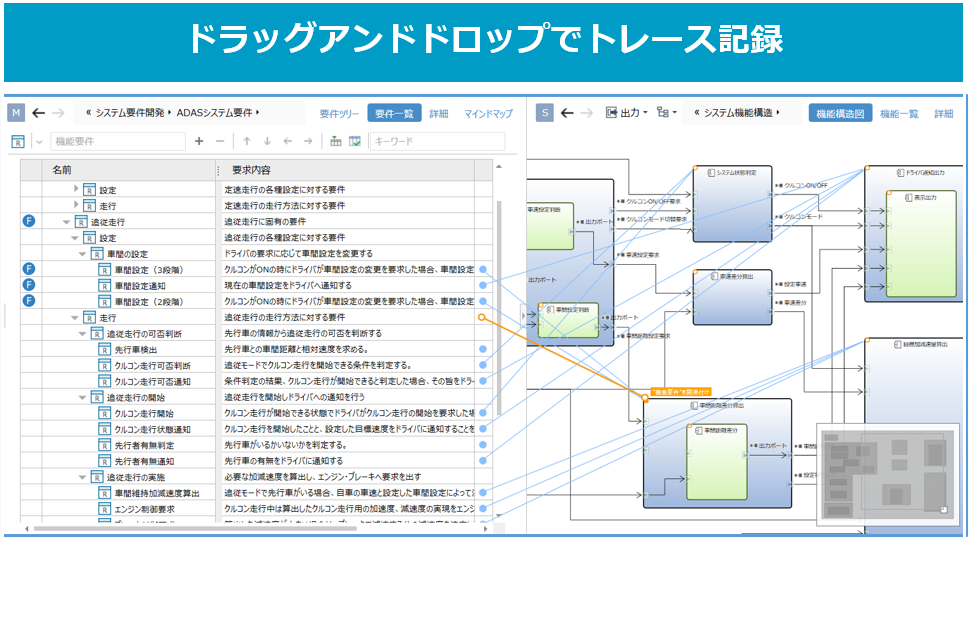

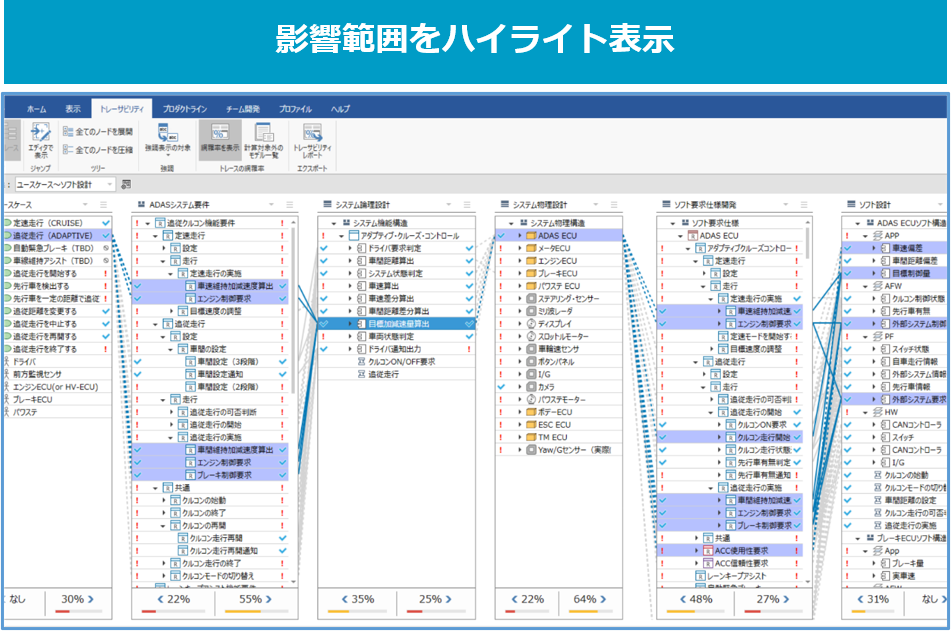

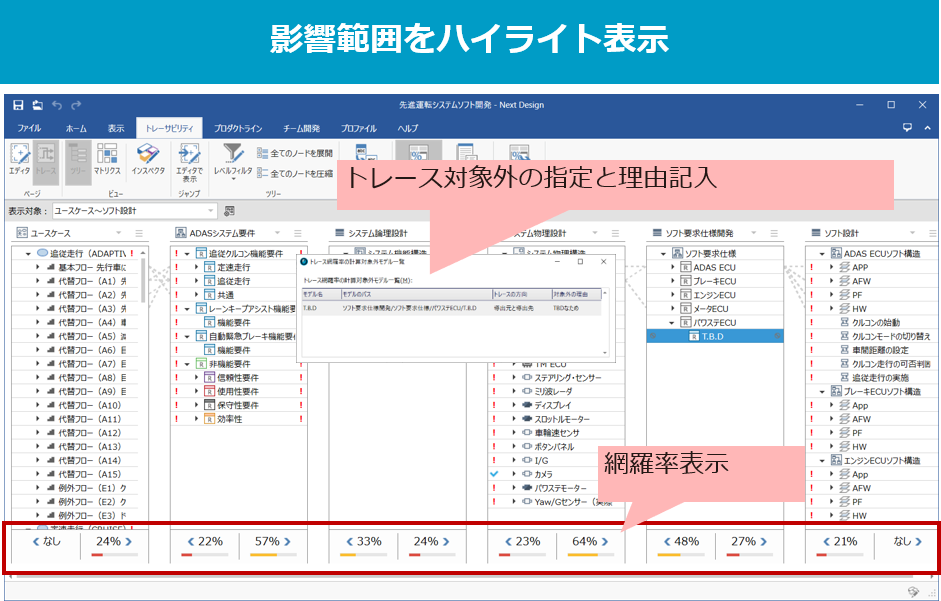

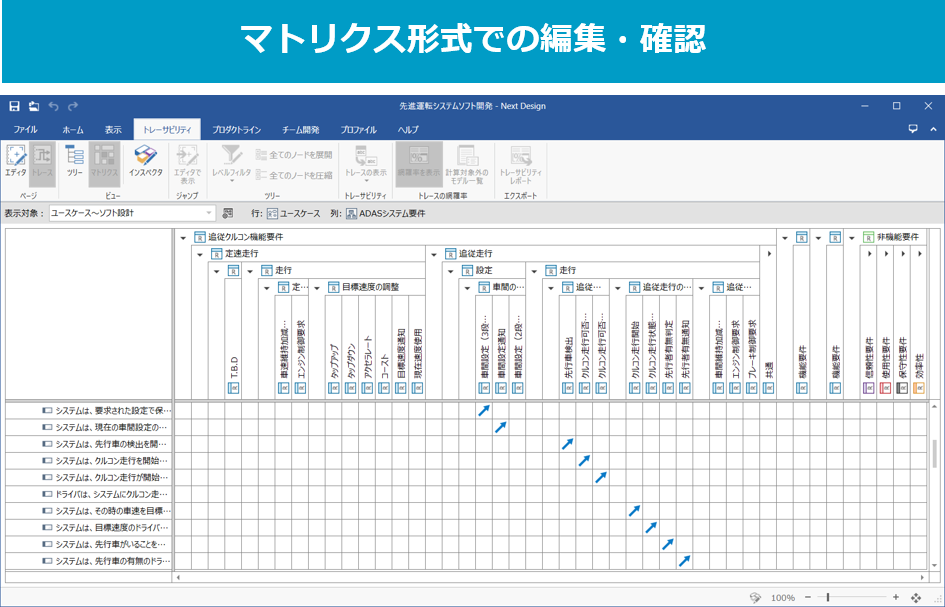

トレーサビリティ自動記録により影響範囲を容易に確認

- ・要求から設計へとドラックアンドドロップで関連情報を割り付けるだけでトレーサビリティを自動記録

- ・選択した要素における影響範囲をハイライト表示でき、確認したい工程に絞って表示させることも可能

- ・マトリクス形式での編集にも対応しているためトレース情報の定義がワンクリック操作で可能

- ・専用ツール並みのトレーサビリティ管理機能を搭載

- ・トレーサビリティの網羅率を表示

- ・トレースの対象外指定および理由記入が可能

- ・要素間トレース関係の有無をアイコン表示

- ・ワンクリックで設計画面にジャンプ

- ・Excel形式でトレーサビリティレポート出力が可能

- ・複数パターンのトレーサビリティツリー表示が可能

|

|

|

|

※クリックすると拡大画像が表示されます。

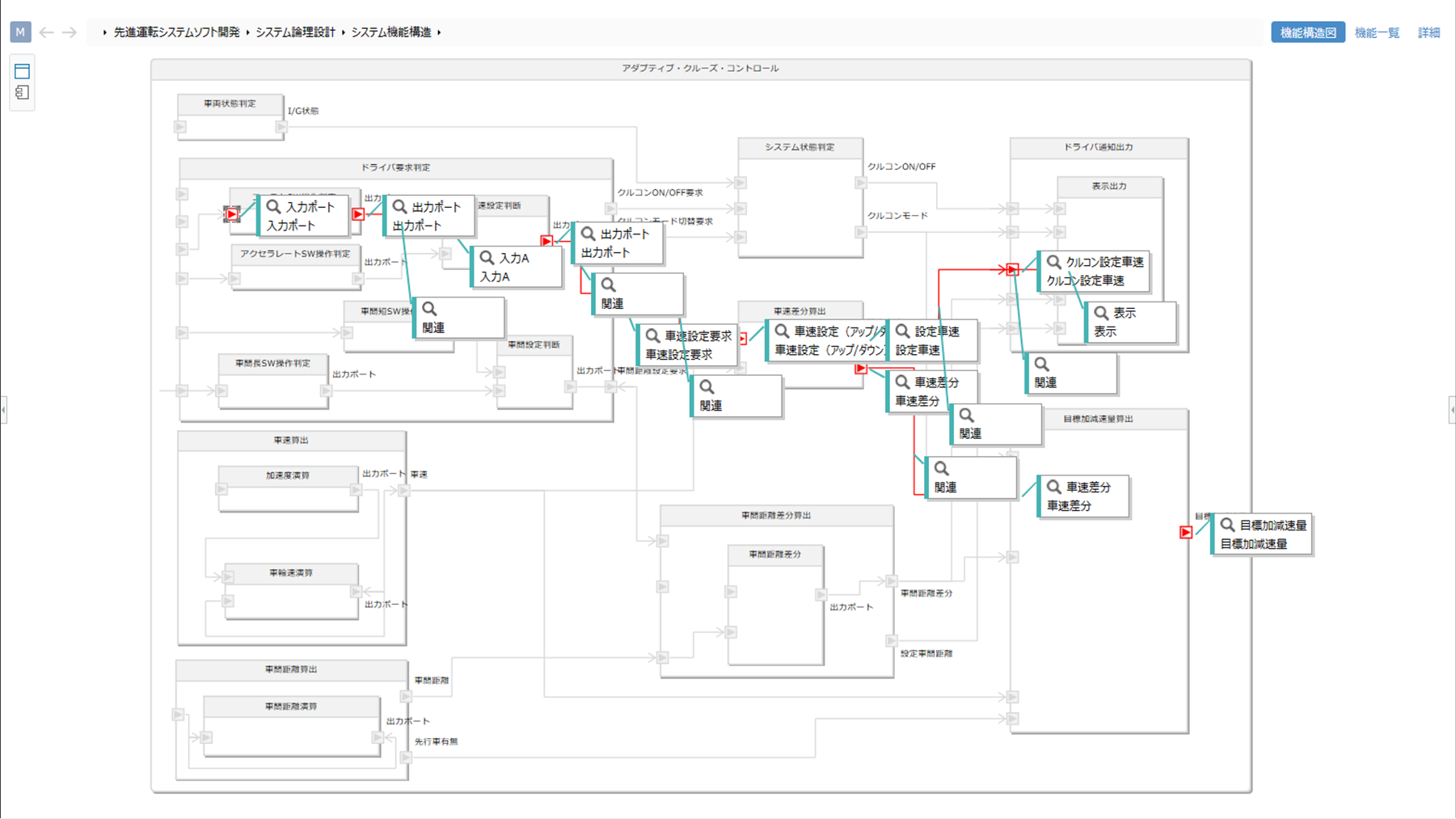

エクステンション利用で設計内容チェックやツール連携を自動化

- ・ユーザーが自由にエクステンションを開発して独自の設計ツールへ機能拡張することで設計作業の自動化が可能

| 機能安全にも適用できるエクステンション開発例 |

|

● データフロー解析

|

|

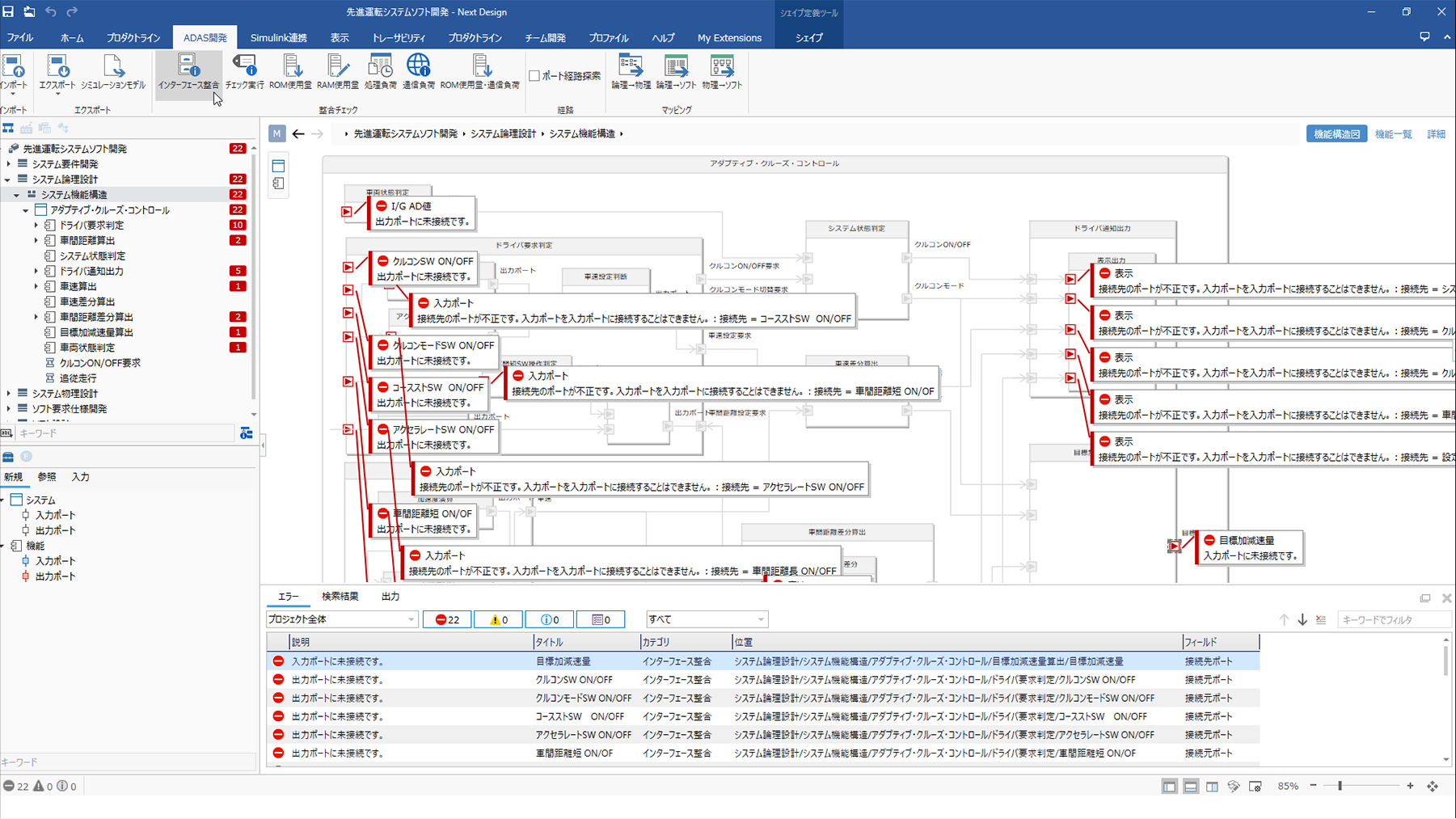

● インタフェース整合チェック

|

|

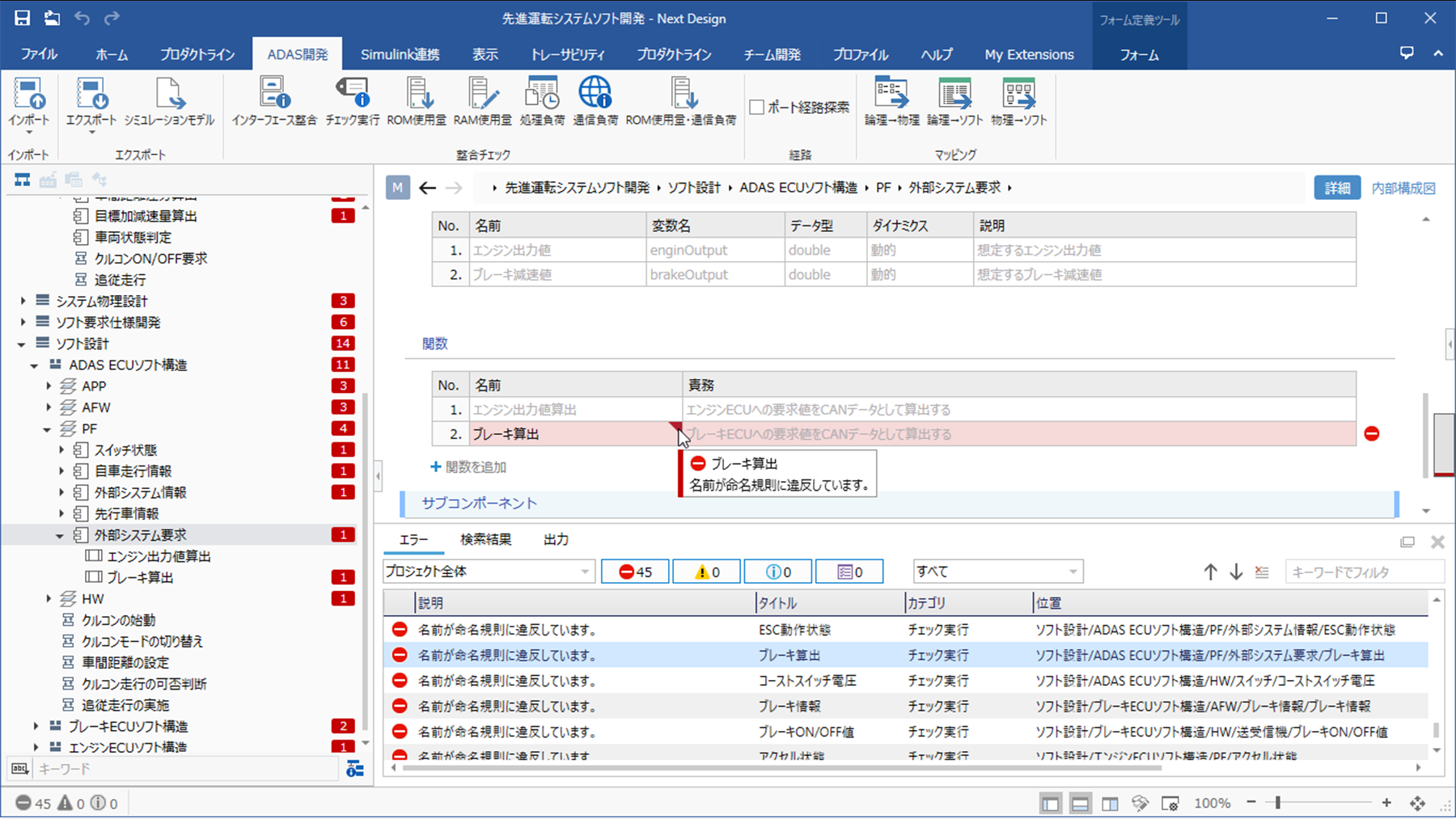

● 固有命名規則のチェック

|

|

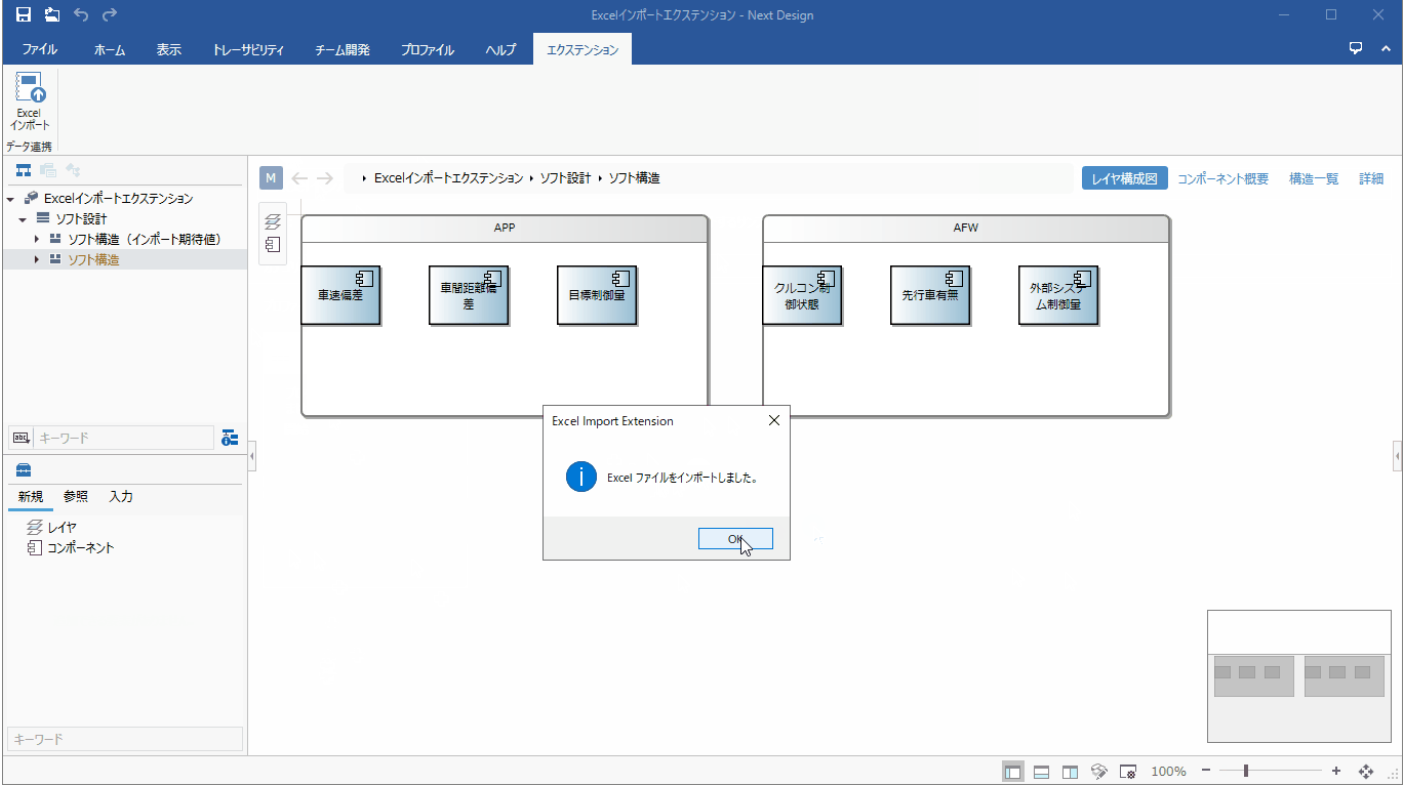

● 既存設計データのインポート

|

※クリックすると拡大画像が表示されます。

関連資料

関連ブログ

以下のリンクからブログ記事をご参照いただけます。

INDEX

- 1. Next Designトップ

- 2. Next Design詳細

- 3. 事例紹介

- 4. V4.0新機能の紹介